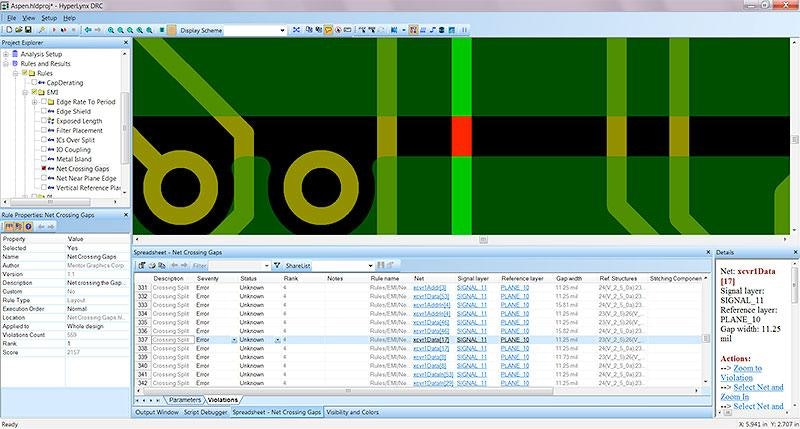

Shaughnessy: What questions are you hearing from hardware designers who are tackling these types of designs?įerry: The latest version of HyperLynx's new capabilities provides solutions to system-level designers with hard questions along these lines. Shaughnessy: What does it take to validate high-speed serial interface from chip-to-chip in a large system? It seems that it would be a real issue with a data center or cellular base station.įerry: To validate a high-speed serial link end-to-end per modern protocol every aspect of the signal interconnect between the chips must be modeled accurately including the IC packages, trace interconnect, as well as the characteristics of the drivers and receivers, including complex equalization schemes and optimization capabilities associated with those. For example, the new standards rely on new metrics such as channel operating margin (COM) to determine the pass or fail criteria of the interconnect. Some of the challenges hardware designers face with the recent protocols are related to differences in the types of analysis that are required and the results they must understand to properly determine if a interface will pass or fail the requirements for that given protocol. Often with each new generation of protocol, the data rates are doubling. The number of protocols for high-speed serial data has increased drastically in the last few years. What do you see going on in the SERDES standards space?Ĭhuck Ferry: SERDES-related standards have been evolving very quickly. Part of the problem with SERDES seems to be that the standards for SERDES have been playing catch-up for a while, according to quite a few design engineers. I spoke recently with Chuck Ferry, product marketing manager with Mentor, about the new HyperLynx and some of the new serial link design capabilities that customers have been demanding.Īndy Shaughnessy: Some of the newer HyperLynx capabilities are focused on the users’ SERDES design challenges.

This version may be the first SI tool in the industry to fully automate SERDES design channel validation. Mentor recently released the newest version of its HyperLynx signal integrity software.

0 kommentar(er)

0 kommentar(er)